# 54ACT823 9-Bit D Flip-Flop

## **General Description**

The ACT823 is a 9-bit buffered register. It features Clock Enable and Clear which are ideal for parity bus interfacing in high performance microprogramming systems. The ACT823 offers noninverting outputs and is fully compatible with

## Logic

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

## AC Electrical Characteristics (Continued)

| Symbol           | Parameter             | V <sub>CC</sub> (V) (Note 4) | $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$ $C_L = 50 \text{ pF}$ |      | Units | Fig.<br>No. |

|------------------|-----------------------|------------------------------|----------------------------------------------------------------------|------|-------|-------------|

|                  |                       |                              | Min                                                                  | Max  |       |             |

| t <sub>PLH</sub> | Propagation Delay     | 5.0                          | 1.0                                                                  | 12.0 | ns    |             |

|                  | CP to O <sub>n</sub>  |                              |                                                                      |      |       |             |

| t <sub>PHL</sub> | Propagation Delay     | 5.0                          | 1.0                                                                  | 12.0 | ns    |             |

|                  | CP to O <sub>n</sub>  |                              |                                                                      |      |       |             |

| t <sub>PHL</sub> | Propagation Delay     | 5.0                          | 1.0                                                                  | 18.0 | ns    |             |

|                  | CLR to O <sub>n</sub> |                              |                                                                      |      |       |             |

|                  | Output Enable Time    | 5.0                          | 1.0                                                                  | 11.5 | ns    |             |

|                  | ŌĒ to O <sub>n</sub>  |                              |                                                                      |      |       |             |

| ·                | Output Enable Time    | 5.0                          | 1.0                                                                  | 12.0 | ns    |             |

|                  | OE to O <sub>n</sub>  |                              |                                                                      |      |       |             |

| I .              | Output Disable Time   | 5.0                          | 1.0                                                                  | 13.5 | ns    |             |

|                  | OE to O <sub>n</sub>  |                              |                                                                      |      |       |             |

| t                |                       |                              |                                                                      |      |       |             |

|                  |                       |                              |                                                                      |      |       |             |

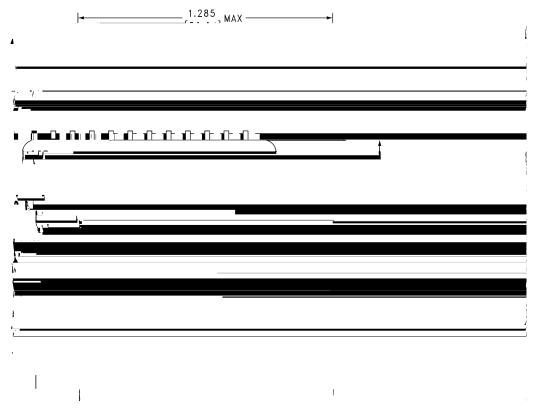

# Physical Dimensions inches (millimeters) unless otherwise noted

24 Lead Ceramic Dual-in-line

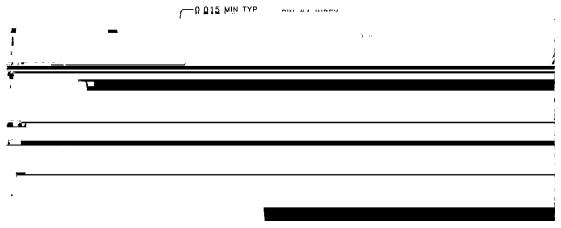

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

28 Lead Ceramic Leadless Chip Carrier Package Number E28A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant